【FPGA图像处理实战】- 图像裁剪

judy 在 周五, 01/19/2024 - 09:55 提交

今天我们来聊一聊FPGA图像处理中图像裁剪功能的实现。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

今天我们来聊一聊FPGA图像处理中图像裁剪功能的实现。

AMD 已针对该公司目前提供的多种可编程逻辑器件发布了产品停产通知

今天详细介绍一下图像处理基础算法---图像处理灰度二值化。

让我们看一下I2S规范,并尝试用FPGA播放音频文件

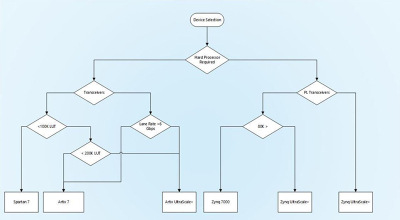

在使用可编程逻辑器件设计时,最重要的步骤之一就是为应用选择最佳器件

今天介绍一下图像处理中的基础算法--彩色图像灰度化。

RGB颜色空间和YUV颜色空间是图像处理中经常遇到的两个颜色空间,但它们的特性不一样

本章节主要学习了两种方法添加ILA以及ILA IP、VIO IP等调试工具的使用方法。

本文将言简意赅的,帮助大家掌握VGA时序的要点,快速掌握和上手。

这里我们先逆推一下CAN总线的一些特点。