【FPGA数学运算】verilog无符号数与有符号数,怎么才能不用错?

judy 在 周四, 11/23/2023 - 09:15 提交

今天我们来聊一聊verilog中的“有符号数”和“无符号数”

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

今天我们来聊一聊verilog中的“有符号数”和“无符号数”

本项目中,我们将使用AMD AC701评估板,在AMD Artix™ 7 FPGA上创建图像处理管道

简单介绍一下xilinx FPGA的DNA,及怎么读取出来

FPGA开发过程中,离不开时序约束,那么时序约束是什么?

我们知道正常的调试器/下载区的JTAG接口可以兼容很多芯片

我们将使用 MATLAB Simulink 和 HDL 编码器创建自定义 IP -- AWB

Nand Flash因其具有容量大、成本低、寿命长的特点,被广泛的用作数据存储的解决方案

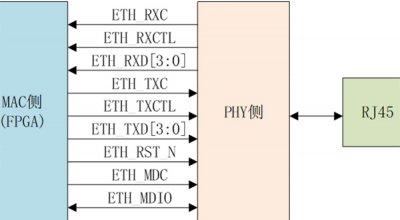

本文继续简单介绍一下基于FPGA的以太网ARP通信

罗彻斯特电子携手AMD/Xilinx,为Xilinx传统FPGA和相关配置PROM产品提供供货支持

主机与目的主机进行以太网通信,需要知道目的主机的MAC地址