FPGA的多bit信号跨时钟域处理方法之一:握手法(必须掌握)

judy 在 周一, 09/04/2023 - 17:01 提交

多bit信号跨时钟域的处理方法之一是握手法,也可以称作应答法

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

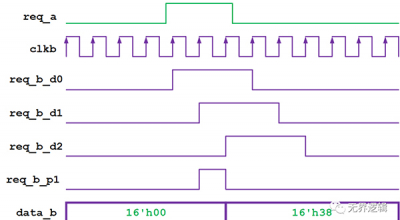

多bit信号跨时钟域的处理方法之一是握手法,也可以称作应答法

Hotchips上的AMD关于全球最大的FPGA分享。

本文分享BRAM资源使用优化策略

本文仅介绍几种常见的基于滤波器的方法的2D去噪

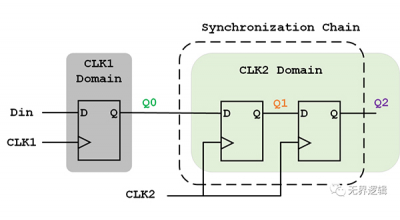

多bit信号跨时钟域如何处理呢?为什么不能使用两级打拍的方式呢?

用支持PYNQ框架的PYNQ-ZU平台,与人工智能来一场聊天

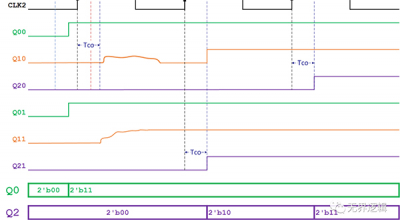

本文重点讲解单bit跨时钟域的处理方法

FPGA属于数字电路范畴,工作中我们会碰到时钟频率,信号速率

详细枚举了FPGA中FIFO的分类和特性

本文考虑了一个具有两个发射天线和两个接收天线的MIMO系统