同步 FIFO、LIFO/Stack

judy 在 周四, 06/15/2023 - 10:38 提交

在这篇文章中,展示了一个简单的 RTL 同步 FIFO

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

在这篇文章中,展示了一个简单的 RTL 同步 FIFO

这里介绍两种常见的设计hash链表的方案

今天的文章让我们来看看当设计不能满足时序要求时如何分析并解决它

ROM的英文全称为Read-Only Memory,即只读存储器。可以从任意地址上读取数据

该项目介绍了如何使用 Verilog 实现具有预生成系数的简单 FIR 滤波器。

在FPGA的设计中,尤其是在通信领域,经常会遇到hash算法的实现

本文概述了芯片设计流程、不同阶段以及它们对创建有效芯片的贡献。

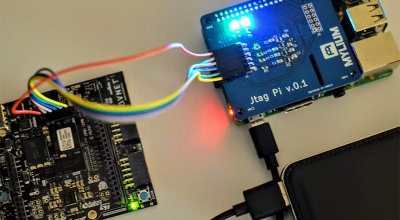

本文使用树莓派+FPGA进行方案验证

如何在 FPGA 中进行简单和复杂的数学运算。

FPGA中的Bank和Clock Region有什么关系?这应该是很多FPGA工程师都很困惑或者没有认真相关的一个问题