科普:FPGA的八种用途

judy 在 周三, 03/01/2023 - 09:47 提交

FPGA由可配置逻辑块与可编程互连相结合的网格构成。制造完成后,FPGA还可以重新编程

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

FPGA由可配置逻辑块与可编程互连相结合的网格构成。制造完成后,FPGA还可以重新编程

搞FPGA的人可能都遇到过这样的问题:以前对外发布的版本的代码找不到了

本次测试内容为基于ARM+FPGA架构的米尔MYD-JX8MMA7开发板其ARM端的测试例程

在这篇 C++ 实现的第一篇文章中,我们开始针对卷积层的 C++ 实现

本文介绍使用 FPGA 实现深度学习的技术

本文将解释“什么是深度学习”和“使用 FPGA 进行深度学习的好处”

创建时钟是针对代码中主时钟而言,创建时钟之前需要知道代码中的主时钟都是什么

目前主流的目标检测算法都是用CNN来提取数据特征,而CNN的计算复杂度比传统算 法高出很多

本文中主要以MP5650为例,来叙述把PGOOD引脚级联至使能引脚来实现排序。

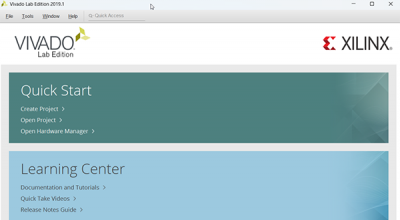

今天讲一讲FPGA单独下载固化文件的几种方式