在 FPGA 上快速构建 PID 算法

judy 在 周一, 04/24/2023 - 09:26 提交

作为一名工程师,在项目实施阶段多多少少会遇到需要使用控制理论的应用程序。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

作为一名工程师,在项目实施阶段多多少少会遇到需要使用控制理论的应用程序。

本文介绍一下使用FPGA实现低延迟的成像系统

在本文中,我们将循环并行化应用于先前任务并行化的推理内核,并平衡层与层之间的执行时间

在本教程中,旨在加深对深度学习和 FPGA 的理解

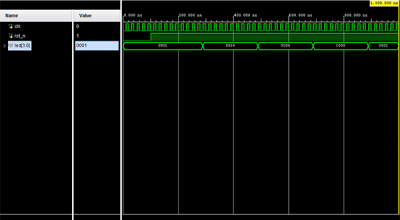

流水灯是大多数学习者接触到的第一个实验,也是非常经典的一个实验,在此,我们一起学习一下流水灯

本篇小文试着从一个SerDes用户的角度来理解SerDes是怎么设计的

本文整理了数字电路课程中的相关基本的知识点和较为重要的知识点,用于求职的数电部分的知识准备

在本文中,我们将结合这些层来创建一个完整的推理函数

FPGA的实现过程可以对综合后生成的网表进行逻辑综合优化、以及布局、布线方面的优化

配置组电压选择引脚必须设置为高电平或低电平,以确定I/O电压支持的引脚在bank0