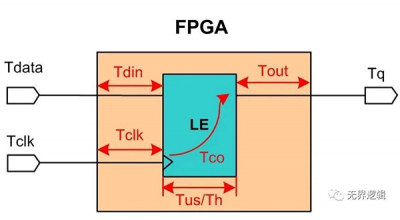

关于FPGA底层的思考:if-else的逻辑延迟一定比case大吗?

yangyf000 在 周五, 08/18/2023 - 09:00 提交

如果case和if-else都是使用一个查找表实现的,那他们的延迟有区别吗?

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

如果case和if-else都是使用一个查找表实现的,那他们的延迟有区别吗?

本文简单介绍一个使用FPGA做的开源示波器

行业报告预测,FPGA 市场预计将从 2023 年的 97 亿美元增长到 2028 年的 191 亿美元

HDL会涉及到标识符,标识符适用于定义常数,变量,信号,端口

本文主要介绍FPGA中常用的RAM、ROM、CAM、SRAM、DRAM、FLASH等资源

需要注意的是,物理器件都是有延时的,包括线延时

本文介绍FPGA 设计工程师需要的 10 项有用技能

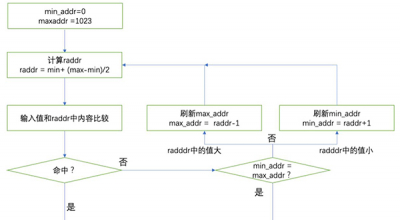

二分法查找算法是在软件中广泛应用的一种算法,那么在FPGA的设计中是否可以用这种算法呢?

项目在上板测试过程中必现报文被丢弃的现象,方案不是很复杂

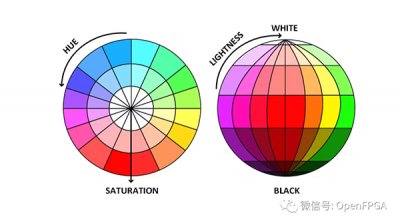

颜色空间转换是图像及视频中常用的解决方案