别乱用 FULL_CASE 和 PARALLEL_CASE

judy 在 周二, 07/05/2022 - 10:58 提交

case语句可以说是我们在FPGA开发中使用频率非常高的一条语句。同时,Verilog还提供了语句 casex 和 casez供我们使用。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

case语句可以说是我们在FPGA开发中使用频率非常高的一条语句。同时,Verilog还提供了语句 casex 和 casez供我们使用。

我们今天要学习的正是由BRAM资源构成的RAM IP核----Block Memory Generator。

Block_RAM应该是每个FPGA开发者经常遇到的,其作为一种固定资源存在于FPGA中,针对xilinx的BRAM,正常通过vivado的IP Core Generator得到

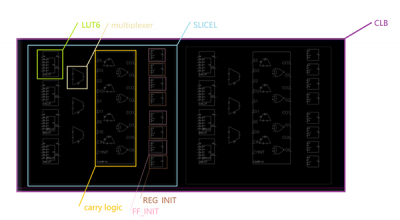

CLB实际上是四种基本元素的集合----查找表LUT,进位链CARRY4,多路选择器Multiplexer以及存储单元FF。

FPGA底层的CARRY4本质上就是用来实现最基本的加、减法运算的,在了解CARRY4之前,我们需要对1bit以及多bit的二进制加法及其FPGA实现做一个了解。

今天给大家介绍一下FPGA上部署深度学习的算法模型的方法以及平台。希望通过介绍,算法工程师在FPGA的落地上能“稍微”缓和一些,小白不再那么迷茫。

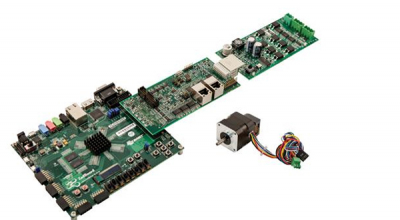

电机在各种工业、汽车和商业领域应用广泛。电机由驱动器控制,驱动器通过改变输入功率来控制其转矩、速度和位置。

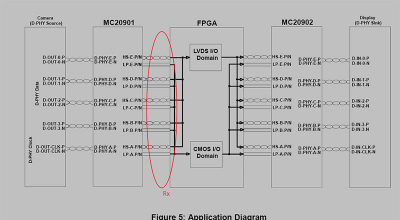

本人比较喜欢Xilinx家的东西,这里就讲一讲Xilinx家的MIPI方案。这里以普通7系列作为讨论的对象, X家高端的KU+/MPSOC+有已经可以直接支持MIPI接口的IO了。

RAM是Random Access Memory的首字母缩写。它是一种主存储器,用于存储当前正在使用的信息。信息可以是正在处理的数据或程序代码。

移位寄存器内的数据可以在移位脉冲(时钟信号)的作用下依次左移或右移。移位寄存器不仅可以存储数据,还可以用来实现数据的串并转换、分频,构成序列码发生器、序列码检测器