Xilinx FPGA时钟及I/O接口规划(二)

judy 在 周四, 06/02/2022 - 10:17 提交

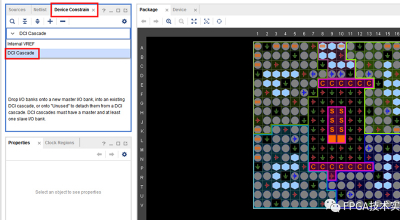

Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。

如果你想要一探Zynq技术,想要在异构平台上实践属于你的项目,想要把软硬件协同设计带入智能时代的前沿领域,欢迎加入我们!

6月9日,上午10:00 – 11:30, AMD Xilinx 携手iWaySense 举行线上直播《看 FPGA 如何赋能传统汽车后视镜》与大家共同探讨这个即将开启的千亿级规模的汽车前装市场。

如何获取Xilinx FPGA的Device DNA呢,下面我从JTAG和调用源语两个方法说明,并开放核心代码供大家参考。

本文主要介绍时钟及I/O规划的各个阶段及流程要点。

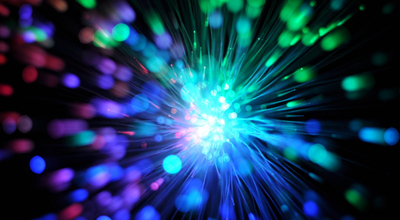

市售常见的基于FPGA的平台产品包括FPGA开发板、FPGA原型验证系统。既然他们同样都是基于FPGA芯片设计的,为什么规模、功能、成本和价格上有非常大的差异?

本文介绍FPGA与X86 CPU高速通信的几种方案

众所周知,中高端FPGA的电源中有两大耗电大户,VCCINT核心电压,和MGT高速收发器,实际工作电流取决于资源使用率、时钟频率、逻辑翻转率等

本文将为大家介绍FPGA原型验证的魅力,以及贸泽电子在售的极具市场竞争力的FPGA产品和相关的开发套件。

在本文中,我们以vivado自带综合器为例、以verilog为编程语言,看看如何理解和利用警告信息排除代码中的小bug。