如何用 QDMA访问OCM

judy 在 周二, 09/03/2024 - 17:01 提交

本文将详细介绍如何通过NOC使用CPM访问片上内存(OCM)

本文将详细介绍如何通过NOC使用CPM访问片上内存(OCM)

数字电路中,小数可以用两种形式来表示:「定点数」和「浮点数」。浮点数的内容我们下篇文章再讲,本文只讲定点数。

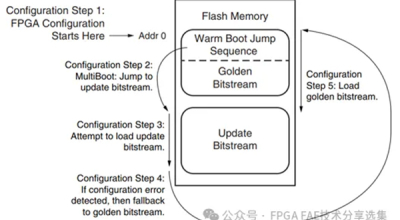

Multiboot是指多镜像启动,比如在FPGA的加载flash里面存放2个或者多个FPGA的配置文件,每个配置文件都可以单独完成FPGA的逻辑配置

本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。

第五代 AMD EPYC 处理器将扩大EPYC在通用和高性能计算工作负载方面的优势,对于科学模拟工作(如NAMD),“Turin”的性能更高

在本周召开的Hot Chips大会上,AMD总裁Victor Peng探讨了半导体行业面临的一个重大挑战,即应对日益增长的AI模型需求所带来的电力问题。

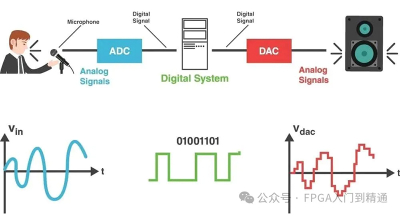

今天,我们将一起探索数字信号处理基础中至关重要的两个概念:连续信号离散化与采样定理。

文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP核相关因素