赛灵思刘珊珊:自适应、可编程平台正在加速工业视觉

judy 在 周二, 06/15/2021 - 10:06 提交

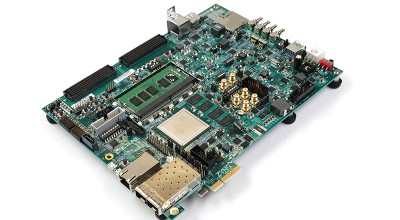

近日GTIC 2021嵌入式AI创新峰会在北京圆满收官!作为下午场唯一家硬件平台厂商代表,赛灵思公司的软件和解决方案市场部高级经理刘珊珊带来了以《MPSoC平台加速工业视觉应用创新》为题的深入分享。

近日GTIC 2021嵌入式AI创新峰会在北京圆满收官!作为下午场唯一家硬件平台厂商代表,赛灵思公司的软件和解决方案市场部高级经理刘珊珊带来了以《MPSoC平台加速工业视觉应用创新》为题的深入分享。

在Xilinx的ZCU102和ZCU106单板设计中,使用了管脚PS_MODE1作为外部USB Phy的复位信号。在MPSoC的文档ug1085和ug1087中,关于PS_MODE1的信息比较少。下面是更详细的描述。

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加功能,支持不同Stride/Pitch(步长)的YUV文件的编码。

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加输出NV12视频的功能。

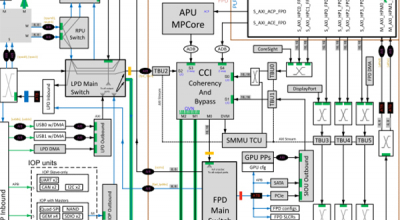

MPSoC的DDR控制器的数据通道上集成了 AXI performance monitors (APM)。具体情况,可以参考Xilinx UG1085 (v2.2)中Chapter 15的“Figure 15‐1: PS Interconnect”或者Figure 17-1。

MPSoC的MAC支持1588。在Linux Kernel的配置项中使能CONFIG_MACB_USE_HWSTAMP,并在Linux rootfs添加Linux ptp/ethtool,就可以运行1588的软件命令ptp4l。

在测试MPSoC VCU的编解码时,经常需要使用NV12 YUV文件。YUV文件很大,所以经常依靠解压MP4等文件来产生NV12 YUV文件。 FFMpeg是一个强大的工具,可以用来从MP4文件生成NV12 YUV文件。

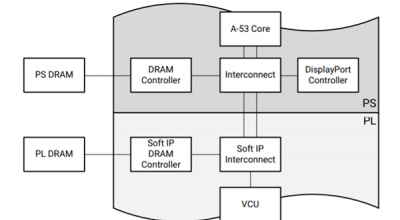

MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线。比如在文件xfsbl_partition_load.c中,FSBL加载FPGA的bit后会执行下列操作,打开PS和PL之间的接口和信号线

赛灵思车规级 XA Zynq®UltraScale+™ MPSoC 平台提供了特有的自适应能力及高性能计算能力,完美契合宏景智驾 ADCU产品需求,促成了其名为“双子星 (Gemini)”的软硬一体化自动驾驶计算平台 ADCU 的成功推出。

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请参考文档APU GIC: CoreLink GIC-400 Generic Interrupt Controller, DDI 0471B, r0p1。