【ZYNQ Ultrascale+ MPSOC FPGA教程】第八章FPGA片内FIFO读写测试实验

judy 在 周四, 12/31/2020 - 09:27 提交

FIFO是FPGA应用当中非常重要的模块,广泛用于数据的缓存,跨时钟域数据处理等。学好FIFO是FPGA的关键,灵活运用好FIFO是一个FPGA工程师必备的技能。本章主要介绍利用XILINX提供的FIFO IP进行读写测试。

FIFO是FPGA应用当中非常重要的模块,广泛用于数据的缓存,跨时钟域数据处理等。学好FIFO是FPGA的关键,灵活运用好FIFO是一个FPGA工程师必备的技能。本章主要介绍利用XILINX提供的FIFO IP进行读写测试。

FPGA本身是SRAM架构的,断电之后,程序就消失,那么如何利用FPGA实现一个ROM呢,我们可以利用FPGA内部的RAM资源实现ROM,但不是真正意义上的ROM,而是每次上电都会把初始化的值先写入RAM。本实验将为大家介绍如何使用FPGA内部的ROM以及程序对该ROM的数据读操作。

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次,实现亮、灭、亮、灭的控制。会控制LED灯,其它外设也慢慢就会了。

很多初学者看到板上只有一个25Mhz时钟输入的时候都产生疑惑,时钟怎么是25Mhz?如果要工作在100Mhz、150Mhz怎么办?其实在很多FPGA芯片内部都集成了PLL,其他厂商可能不叫PLL,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

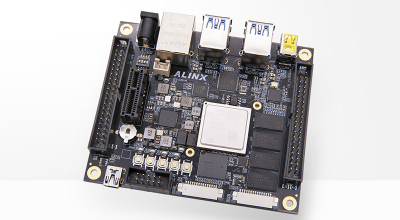

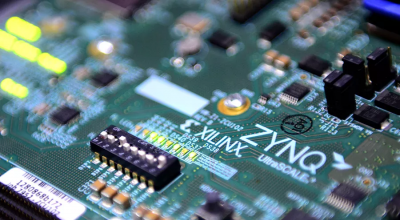

Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平台。其亮点在于FPGA里包含了完整的ARM处理子系统(PS),包含了四核Cortex-A53处理器或双核Cortex-A53加双核Cortex-R5处理器,整个处理器的搭建都以处理器为中心,而且处理器子系统中集成了内存控制器和大量的外设,使处理器核在Zynq中完全独立于可编程逻辑单元

Xilinx为MPSoC支持4种libMali的backend: X11, Wayland/GBM, Fbdev, Headless-EGL。QT支持4种plugin(插件)或者backend,FB,X11,Wayland,eglfs。对不同的plugin(插件)或者backend,QT应用层是一样的。

Zynq-7000和MPSoC有很多MIO管脚。如果外设有中断,也可以通过MIO驱动。

测试环境:Xilinx ZCU106 单板

Xilinx VCU TRD2020.1

Linux 内核配置:根据文档Docker on Zynq Ultrascale+ (Xilinx Yocto Flow),在PetaLinux工程的文件project-spec/meta-user/recipes-kernel/linux/linux-xlnx/user.cfg里添加下列配置项。

刚启动MPSoC的VCU解码器时,解码器先分析码流,得到分辨率信息后再调用回调函数分配buffer。这会耗费时间,增加延迟。如果希望减少延迟,可以使用prealloc-args参数,提前指定视频分辨率信息,提前分配buffer。