Vitis IDE Git 集成快速入门

judy 在 周三, 03/22/2023 - 15:25 提交

本文将探讨如何在 Vitis™ 中使用 Git 集成以及如何使用团队操作来共享 Vitis 工程

本文将探讨如何在 Vitis™ 中使用 Git 集成以及如何使用团队操作来共享 Vitis 工程

Vitis软件平台由适用于交互式工程开发的集成设计环境和适用于脚本化或手动应用开发的命令行工具组成

尽管超声波技术能提供显著优势,但医疗设备制造商正发现

Vitis是Xilinx SDK的继承开发工具,从Vivado 2019.2版本开始启用

Vitis 应用加速开发流程提供了相应的框架,可通过使用标准编程语言来为软件和硬件组件开发和交付 FPGA 加速应用

该方法不仅可帮助开发人员做出有关应用架构的重要决策,而且还有助于确定各种因素

虽然 FPGA 可使用 Verilog 或 VHDL 等低层次硬件描述语言 (HDL) 来编程,但现在已有多种高层次综合 (HLS) 工具可以采用以 C/C++ 之类的更高层次的语言编写的算法描述

在 Vitis 应用加速流程中,在可编程逻辑中实现和最优化 C/C++ 语言代码以及实现低时延和高吞吐量所需的大部分代码修改操作均可通过 Vitis HLS 工具来自动执行。

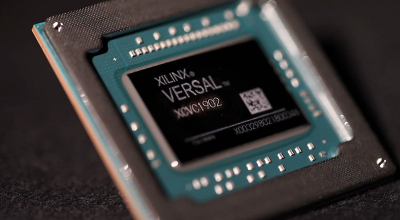

以下是在 Vitis™ 软件平台中创建 Platform Loader and Manager (PLM) elf 文件的步骤。在 Versal™ 器件中,PLM 在 PMC 内执行,并用于引导 APU 和 RPU。