Vitis Model Composer 2023.1现已更新!

judy 在 周三, 05/31/2023 - 15:15 提交

Vitis Model Composer 为 DSP 提供 AMD 系统生成器的所有功能性

Vitis Model Composer 为 DSP 提供 AMD 系统生成器的所有功能性

本实验使用FPGA通过HDMI接口输出彩条、色带、方块等图像。

本实验将为大家介绍如何在Vivado中构建 AXI总线类型的IP核

AMD Vitis 调试代码时,BSP代码的某些应该被执行的行,没有被执行

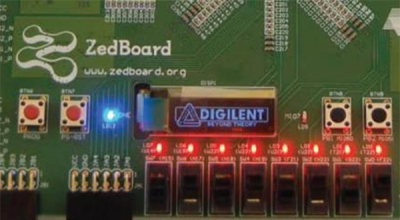

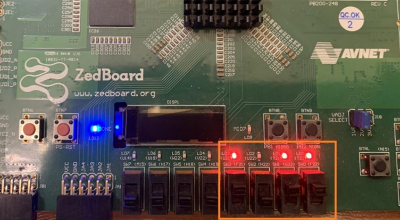

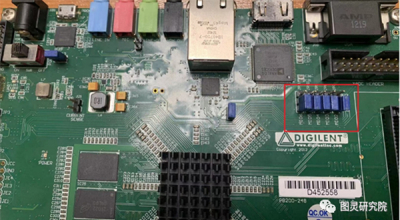

使用ZYNQ最大的疑问就是如何把PS和PL结合起来使用。本实验使用两个AXI GPIO的IP核

AMD Vitis™ 统一软件平台 2023.1 版近期已正式发布!

本实验介绍如何使用ZYNQ芯片PS端的定时器资源

本实验主要介绍使用PS端来完成ZYNQ串口打印输出的功能

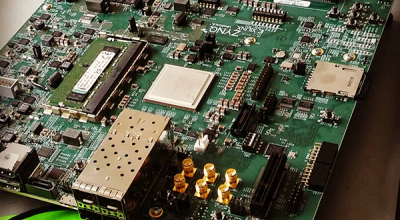

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

本文演示了在Vitis™ 中对 Linux 应用程序开发的过程中如何使用外部库