使用 Vitis 进行嵌入式设计开发用户指南

judy 在 周三, 01/08/2025 - 17:07 提交

AMD Vitis™ 工具套件包含多种设计技术,用于开发以 AMD 器件为目标的异构嵌入式应用。

AMD Vitis™ 工具套件包含多种设计技术,用于开发以 AMD 器件为目标的异构嵌入式应用。

全新 AMD Vitis 统一软件平台 2024.2 版本已于近期推出。系统架构师和开发人员可以借助新版本进一步提升其设计开发流程,同时提高整体系统性能。

全新 AMD Vitis™ Unified Software Platform 2024.2 版本推出。系统架构师和开发人员可以借助新版本进一步提升其设计开发流程,同时提高整体系统性能

在本次网络研讨会中,我们将深入探索 Vitis™ Unified IDE的新特性,并展示过滤器和加密模块的实际应用示例。

通过新版本,系统架构师和开发者可以进一步优化设计开发流程,同时提升整体系统性能。

Vitis 2023.2是Vitis开发工具变化较大的一个版本,设计流程和界面发生了变化。今天介绍一下Vitis New IDE的一个新功能。

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。

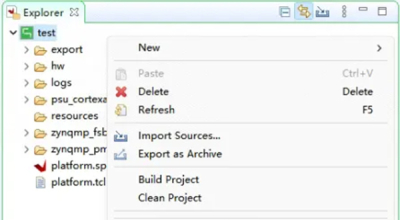

在使用Vitis开发时,当硬件设计发生变化时,这时就需要更新xsa文件。

独立的Vitis嵌入式安装程序提供简单的工具安装,下载量减至大约10GB,安装量减至大约15GB

本文主要介绍OpenCV在Windows 10上的安装和设置。