Vitis 2020.x - Ubuntu GDB内核调试

judy 在 周日, 04/24/2022 - 14:35 提交

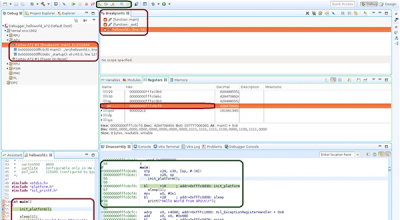

在Ubuntu系统中,当试图在内核代码中设置断点的加速应用程序上运行仿真调试时,工具不会在断点上停止,而只会在主机代码断点上停止。

在Ubuntu系统中,当试图在内核代码中设置断点的加速应用程序上运行仿真调试时,工具不会在断点上停止,而只会在主机代码断点上停止。

我在一个自定义平台上运行我的项目,而我的目标平台的Vivado项目在Vivado合成中使用了以下额外选项。当我运行Vitis链接器时,我看到以下错误。

本章描述了对您所执行的设计流程可能出现的各种问题进行调试的方法。

Vitis 嵌入式平台创建所需要注意的问题

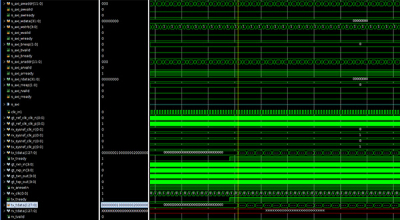

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍

在搭建完Block Design以及硬件代码后,生成bit;bit文件生成成功后,点击Export Hardware,导出xsa文件:(xsa做连接使用)

从官网能够很轻松的下载到vitis的安装包,可以下载Installer进行自动下载安装,也可以下载整个文件的压缩包,通过其中的setup进行安装。

本期主要介绍Vitis/ViTis AI的相关应用技巧和赛灵思应用商城的介绍,以及Versal AI引擎的资源和应用详解。

在Zynq开发时,在Vivado中新建Zynq硬件平台,加入DMA、AXI接口模块,在进行构建软件系统之前,通常需要对硬件平台进行验证,检测模块新建过程中是否存在问题。下面对这一过程进行简单介绍。

Vivado 2019.2开始就没有SDK了,需要在Vitis上创建应用工程。网上大部分都是创建Platform Project再创建Application Projet,然后在Application Projet里导入平台文件。其实一个简便的方法是直接创建Application Projett导入平台文件。