Vitis™ 视频分析 SDK,将视觉化为强大的洞察力

judy 在 周一, 11/08/2021 - 14:35 提交

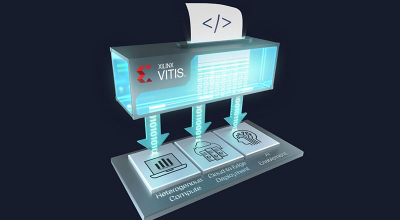

Vitis™ 视频分析 SDK 旨在 Xilinx 目标平台或您自己的平台上构建和部署支持人工智能功能的智能视频分析解决方案的完整软件堆栈。

Vitis™ 视频分析 SDK 旨在 Xilinx 目标平台或您自己的平台上构建和部署支持人工智能功能的智能视频分析解决方案的完整软件堆栈。

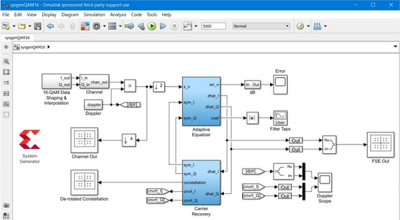

本文描述如何执行基于模型的设计,在 Simulink 环境中实现快速设计探索,并通过自动代码生成加速 Xilinx 器件的生产路径。

学习如何在 ZCU104 评估板上使用 VCU、DPU 和 PL 来构建和运行视频分析示例应用。

本文对vivado、vitis、petalinux2021.1版本以及Vitis AI 1.4安装过程进行详细描述,并提供安装软件网盘地址。

如何将Vitis AI Library应用加入Vitis进行编译,生成可执行文件?

本文描述了在Vivado IDE环境中使用MATLAB和Simulink的DSP附加组件。

本视频展示了如何使用智能模型选型示例开始使用 VVAS。

VVAS 是一个完整的软件堆栈,用于在所有 Xilinx 平台上构建基于 AI 的智能视频分析解决方案!在短短几周内实现从概念到实时部署。

在Vitis下运行DNNDK例程时,(例程地址https://github.com/Xilinx/Vitis-In-Depth-Tutorial/blob/2020.1/Vitis_Plat...)运行到编译时,(20 Right click the hello_dpu project folder and select Build Project)一直出如下错误

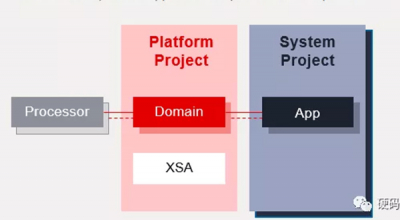

Vitis统一软件平台将Xilinx各种软件统一,即支持Vitis嵌入式软件开发流程,又支持Vitis应用软件加速开发流程。本文介绍Vitis嵌入式软件中的linux应用程序开发流程。