Vivado Design Suite Tcl 命令参考指南

judy 在 周五, 11/25/2022 - 17:41 提交

本指南涵盖了以下设计流程:硬件、IP和平台开发。

本指南涵盖了以下设计流程:硬件、IP和平台开发。

跨时钟域设计(CDC)是个老生常谈的问题,各种笔面试都很喜欢考。其场景很多很杂

最近遇到了一个vivado的报错,也算是一个比较低级的错误了,但是有值得思考的地方,这里分享下。

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

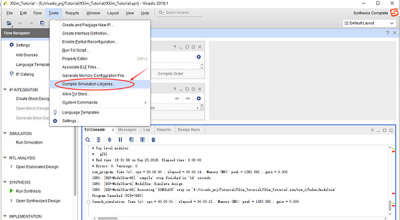

vivado软件切换使用modelsim仿真时,如果出现如下图所示情况

本文主要介绍三个部分:DFX的基本流程、AS的环境搭建、AS的具体执行

Abstract Shell最大的优势是除第一次外,后续可以减少bit的生成时间

在Windows下Vivado默认使用的是2线程,编译较慢。可改为32线程使Vivado可使用更多计算机资源,以加快编译速度

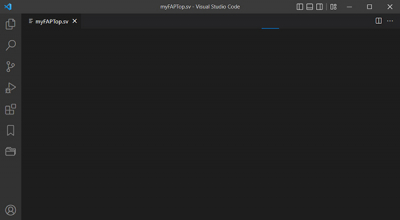

本文将介绍如何在Vivado中将代码编辑器绑定为第三方编辑器——Vscode

Vivado® Design Suite 可提供围绕 IP 的设计流程,支持您将来自各种设计的 IP 模块添加到自己的设计中