Vivado从此开始(进阶篇)读书笔记——跨时钟处理

judy 在 周四, 09/08/2022 - 09:29 提交

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器的方式完成跨时钟域操作

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器的方式完成跨时钟域操作

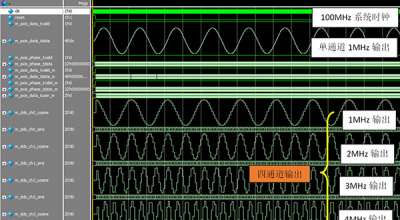

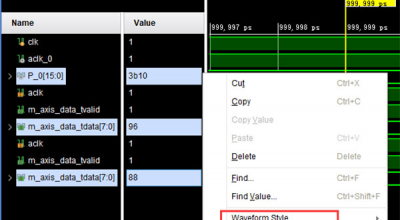

本文我们通过例化Xilinx公司的DDS IP核来产生混频器本振输入频率,并给出Modelsim仿真测试结果。

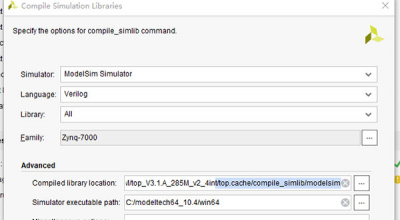

如果只是纯的.v文件仿真那很容易操作,主要是涉及到IP核,那么就必须要对vivado的IP核的库文件进行编译

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

Vivado 中的 sigasi 功能特性使用高速缓存,有时高速缓存大小可能高达数百 MB,导致主目录中存储器减少,从而影响 Vivado 性能。

在设计代码的时候,大部分人都是习惯于使用外部的编辑器进行设计,而不是使用vivado自带的编辑器

通常对FPGA下载程序时,会采用JTAG口下载,完成好HDL设计,并且验证无误后,对设计文件进行综合,布局布线以及生成比特流文件

首先新建ddr的IP,具体每个参数的含义,可以参考之前写的《Virtex7 Microblaze下DDR3测试再右键》,打开IP的Example Design

DFX功能实际上就是部分可重配置功能,开启可重配置功能时,FPGA内部的逻辑可以分割为两种不同类型

12代酷睿CPU在win10、11下一些问题经过的解决方法(经过实践的)