Vivado 中ibert的使用

matt z 在 周四, 10/20/2022 - 16:42 提交

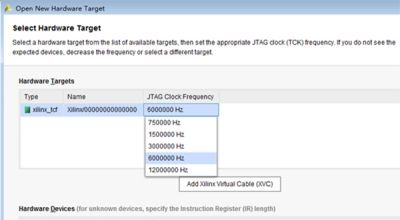

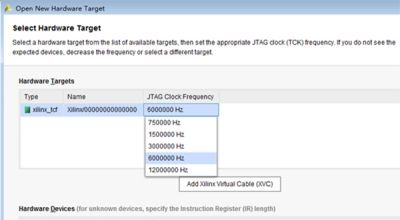

通过Vivado 自带的ibert工具可以对FPGA的GT进行板机的硬件调试。

通过Vivado 自带的ibert工具可以对FPGA的GT进行板机的硬件调试。

vivado有project模式和non-project模式,project模式就是我们常用的方式

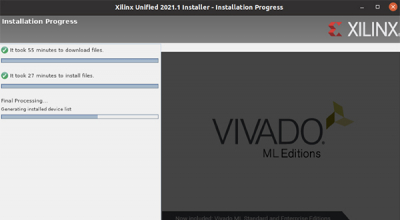

在ubuntu上安装vivado2021.1时,一直卡在最后一步:generating installed device list

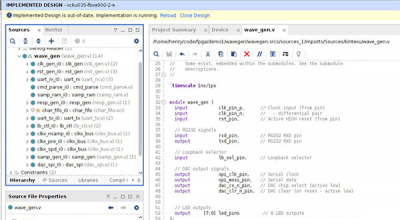

我们在编译FPGA工程的时候一般需要对版本号的更新,一般来说都会有一个日期或者时间的版本标识

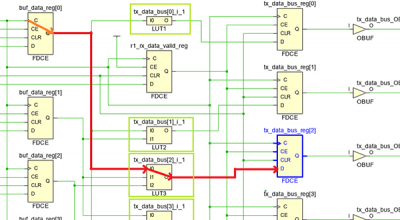

本篇文章我们将通过vivado工程实例来向大家介绍如何读懂时序分析报告。

RS码是一种常用的纠错编码,本文主要介绍如何在vivado环境下利用RS IP核实现RS码的编译码。

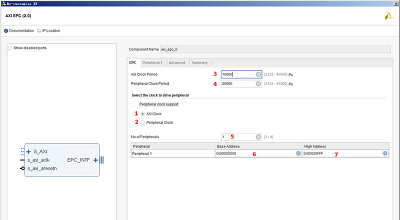

Xilinx FPGA 内嵌的 CPU ,可以通过 AXI EPC 在 FPGA 芯片外接多个多种外设芯片

在本实践中,我们将实际实现 HLS 组件作为 FPGA 设计的一部分

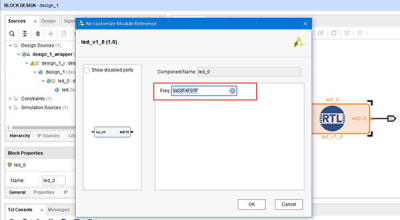

用Vivado开发ZYNQ时,常用到Block Design。Block Design中不仅仅可以添加IP核

在对工程进行综合时,出现综合过程中出现中止或者完全不启动综合,类似下图,明明点击综合启动了几分钟