Vivado爬坑指南(1)

guanxiao_505740 在 周三, 07/05/2023 - 08:59 提交

作为一名刚入坑的新手小白,我将分享自己的一些建议

作为一名刚入坑的新手小白,我将分享自己的一些建议

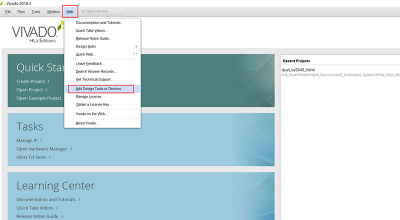

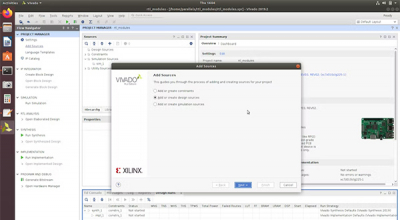

打开vivado,选择help,点击Add Design Tools or Devices

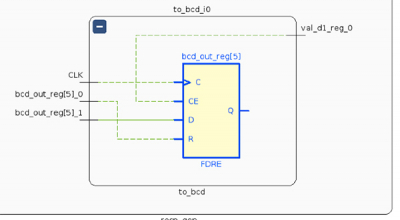

Vivado Schematic中的实线和虚线有什么区别?以下图为例

在Vivado的IP Catelog中找到IBERT,此处以UltraScale Plus系列的GTY为例

使用Intelligent Design Runs,Versal™ 自适应 SoC 的平均 QoR 提升 8%

当我尝试在机器上安装 Vivado 时,无法通过帐户身份验证检查。为什么会出现此问题?

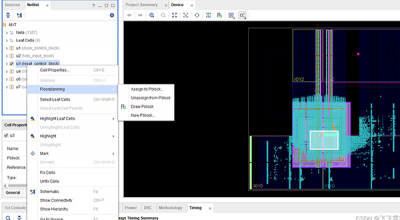

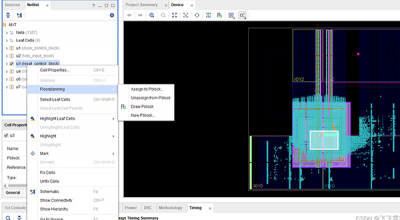

最近在上板测试的过程中,使用mark_debug跑工程后生成的bit在下载的时候遇到了问题

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题,不知道大家有没有遇到

本文介绍vivado 的仿真模式

当使用第三方综合器比如 Synopsys® Synplify Pro或Mentor® Graphics Precision 来综合