Vivado自定义IP核

judy 在 周四, 10/12/2023 - 09:58 提交

本文介绍了在Vivado中创建自定义IP核的步骤

本文介绍了在Vivado中创建自定义IP核的步骤

本文将介绍Vivado中XCI与XCIX文件以及如何使用Core Container打包IP核

打开 Vivado ,进入 Vivado 界面后,点击“ Quick Start ”

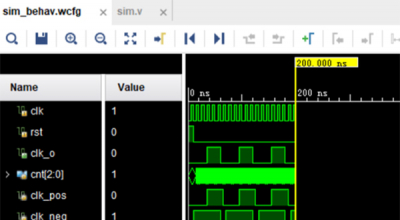

本文将详细介绍Vivado自带仿真器的主要特性

Vivado 软件提供了HDL编写中常用的示例

本文总结了Vivado 2023.1 中针对不同 Versal PCIe IP 的 10 位标签请求器功能的支持信息

本文介绍了如何使用Verilog HDL实现ROM和RAM

本文主要学习了两种仿真方法,并且分别对工程进行仿真。

本文演示如何快速上手AMD-FPGA开发工具软件vitis-vivado

本文将介绍如何清理Vivado工程,并避免缺失必要的文件。