zynq裸核FSBL

demi 在 周五, 09/06/2019 - 16:41 提交

话不多说,进入今天的主题:生成zynq裸核启动文件。1、首先在vivado SDK中分别建立两个工程;2、配置Core1即从核中的BSP文件;3.配置Core0和Core1的DDR空间分配;4.建立FSBL文件,并配置main()文件;5.生成mcs文件和烧写mcs文件到QSPI Flash;6.完成操作将.MCS文件烧写进板子里

话不多说,进入今天的主题:生成zynq裸核启动文件。1、首先在vivado SDK中分别建立两个工程;2、配置Core1即从核中的BSP文件;3.配置Core0和Core1的DDR空间分配;4.建立FSBL文件,并配置main()文件;5.生成mcs文件和烧写mcs文件到QSPI Flash;6.完成操作将.MCS文件烧写进板子里

上篇中我们简单了解了XADC和其基本使用方法,本文我们将学习XADC的报警功能和中断的使用方法。程序中我们设置温度和VCCPAUX的上、下报警阈值。当超出这个范围时,便进入中断进行报警提示。

异常中断发生时,程序计数器PC所指的位置不同,异常中断就不同。中断结束后,中断不同,返回地址也不同。但是,对于系统复位中断,不需要返回,因为整个应用系统就是从复位中断中开始的。

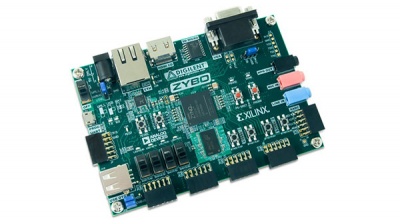

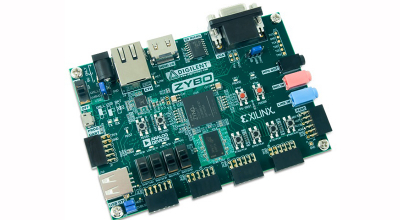

随着开源的MCU源代码越来越多,也逐渐的影响着嵌入式系统开发的思路,出现了两种以前不常见的设计思路。第一,原本需要购买一颗MCU芯片的设计,现在直接考虑购买一颗带有MCU硬核的FPGA(如ZYNQ系列FPGA)替代,既有MCU的功能,又有接口可编程的能力,更加的灵活......

本文将介绍如何在PS中调用Zynq内部的XADC模块进行片内温度和电源电压测量。先了解XADC的相关知识,再通过实例体会XADC的用法,学习XADC API函数的使用。

ZYNQ有专用的DDR Controller接口,如果外部硬件连接了DDR器件,于是在ZYNQ Processing System中正确配置了相应的信号和参数后,DDR就可以成为ZYNQ的内存,在SDK中可以直接使用memcpy、memset以及类似的函数对于Memory空间进行操作。

ZYNQ学习过程中一个重要环节是进行调试,当然在SDK中进行调试时,设置断点进行单步调试非常高效。但是ZYNQ中毕竟涉及到FPGA的硬件部分,于是如果可以通过UART与ZYNQ器件进行双向的通信会使得调试非常方便。

前面我们已经学习了TCP的所有发送、接收和各种回调函数。本文将介绍最后一部分,TCP的轮询机制。在前面TCP发送Hello World的实例中,我们是在main函数的while循环中每隔1s调用一次数据发送函数。本文的实例将利用轮询机制完成同样的功能。

ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS和PL的相互通信通过两个通路完成,分别是GP(General Purpose)Ports和HP(High Performance)Ports。GP Ports包含2个Master接口和2个Slave接口,符合标准的AXI协议数据位宽是32bit。HP Ports包含4个接口,全部是PL作为Master

前两篇我们学习了TCP的发送,本文学习如何处理接收数据。本文使用TCP设计一个echo服务器,开发板将来自所有IP地址和端口的数据原路发送回去,功能和本系列第15篇的UDP echo服务器相同。本文实例与SDK提供的“lwip echo server”例程相比要简化许多,没有使用DHCP协议。本文主要是学习TCP的接收回调,DHCP的内容会在后面专门讲述。