利用ZYNQ SOC快速打开算法验证通路(1)——MATLAB浮点数与定点二进制补码互转

judy 在 周四, 09/20/2018 - 17:35 提交

作者:没落骑士

作者:没落骑士

作者:Steve Leibson

深入了解 Zynq SoC 在基于“OPC UA over TSN”的智能工厂自动化中的作用。

作者:OpenSLee

1 背景知识

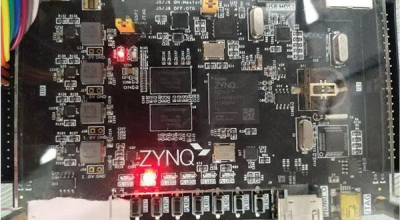

ZYNQ简介

作者:Steve Leibson

很多嵌入式设计使用基于微处理器和微控制器的单板计算机 (SBC) 和系统级模块 (SoM)(例如,请参阅“使用 Raspberry Pi 3 构建低成本工业控制器”)。但是,更多嵌入式应用无法忍受与软件相关的响应时间所带来的延迟。

作者:圆宵,来源:FPGA那点事儿

没接触zynq之前,只用过FPGA,在FPGA中用verilog编程简单明了,后来稍微学习过一点nios ii,就在FPGA中也用过一点点nios ii。所以在刚接触zynq的时候,我就感觉zynq跟altera的FPGA和nios ii的编程肯定会有一些相似的地方。

1.添加debug核的合理方法是在源代码中添加(*mark_debug="true"*),综合后,打开综合结果,set debug内这些标记的信号全部在网标内,不会被优化掉。如果不在代码里加这些标记,直接在综合结果里添加net,很多感兴趣的信号会被优化掉,且残缺不全。

一、嵌入式Linux系统组成