PYNQ系列学习(五)——Jupyter Notebook介绍

judy 在 周四, 12/13/2018 - 17:24 提交

在前面几期的学习中,我们对于PYNQ的环境配置做了较为详细的介绍,并对PYNQ与ZYNQ的异同点做了较为深入的探究。我们知道,PYNQ = Python + ZYNQ,即将ZYNQ部分功能的Python化,直接调用Python库和FPGA硬件库进行功能的开发,典型的例子便是PYNQ_z2开发板

在前面几期的学习中,我们对于PYNQ的环境配置做了较为详细的介绍,并对PYNQ与ZYNQ的异同点做了较为深入的探究。我们知道,PYNQ = Python + ZYNQ,即将ZYNQ部分功能的Python化,直接调用Python库和FPGA硬件库进行功能的开发,典型的例子便是PYNQ_z2开发板

文章是对官方文档Resource Manger部分的总结,写得不是很有条理,仅是自己对这部分学习认识的一个总结,希望对看到的人有所帮助。

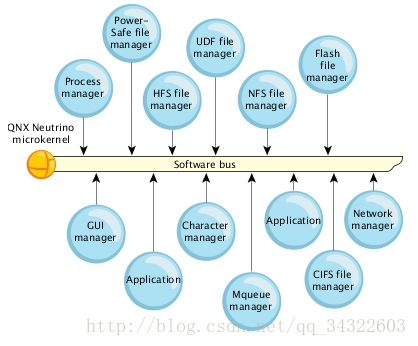

QNX OS是微内核操作系统,其内核仅仅提供进程调度、进程通讯等服务。文件访问、设备驱动等服务都属于用户空间的任务,下图是QNX系统的架构图

除了内核外其它所有进程都属于用户空间,内核作为一个软件总线,将其它所有资源互相连接起来,这种结构看起来像一个团队而不是层次结构,几个相同等级的“player”通过内核相互协调完成任务。

总的来看,资源管理器就是一个在文件系统名称空间中注册了一个名称的进程。其它进程使用其路径来与资源管理器通信。

资源管理器通常用来向各种各样类型的设备提供接口,涉及到管理实际的硬件设备。在其它操作系统这个功能作用通常归为设备驱动。但在QNX系统中,资源管理器不像是设备驱动,它是从内核中剥离出来,看起来就像其它用户级程序一样。若我们需要针对自己的板卡驱动硬件,这个驱动程序的开发就是资源管理器的开发。

上一节我们体验了一把PS和PL是怎样联合开发的,这种ARM和FPGA联合设计是ZYNQ的精华所在。这一节我们实现一个稍微复杂一点的功能——测量未知信号的频率,PS和PL通过AXI总线交互数据,实现我们希望的功能。

如何测量数字信号的频率

最简单的办法——在一段时间内计数

在我们设定的时间(Tpr) 内对被测信号的脉冲进行计数, 得Nx, Fx=Nx/Tpr。

Tpr 越大,测频精度越高。这种方法适合于高频信号,因为这里可能会有一个被测信号周期的误差,测量高频信号时误差小。

另一个变种——在一个周期内计数

在 被测信号一个周期内对基准时钟信号计数,得Nx, 基准时钟周期为T, 则Tx=T*Nx, Fx=1/Tx。

被测信号频率越低, 基准时钟频率越高,测量精度越高。因此这种方法适用于低频信号。

二者结合——多个周期同步计数

QNX版本:QNX6.6

宿主系统:Windows

交互系统:Debin

开发板:MIZ702 完全兼容ZedBoard

前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议的,所以我们实际观察到是AXI_Lite协议的信号时序。

上一期,我们重点学习了ZYNQ的PL开发,本期我们侧重于进行PS开发的学习。我们将在 VIVADO 开发环境下搭建 ARM+FPGA 的系统架构,并在 SDK 中编译软件实现软硬件联合开发。

本部分的学习,我们依旧借助得力的助手与伙伴——PYNQ_z2来完成。

一. 实验目的

1. 点亮开发板右下角三个灯

上一期的学习中,我们系统性地介绍了PYNQ与ZYNQ地区别与联系。PYNQ = Python + ZYNQ,即将ZYNQ部分功能的Python化,直接调用Python库和FPGA硬件库进行功能的开发。

参考

书籍《RapidIO The Embedded System Interconnect》

xilinx手册pg007《Serial RapidIO Gen2 Endpoint v4.1 LogiCORE IP Product Guide》

Zynq-Linux移植学习笔记之14-RapidIO驱动开发

为了快速实现算法板级验证,PC端需要通过JTAG或以太网与FPGA形成通路。最简单便捷的方案是利用协议栈芯片,用户可以无视底层,利用简单的SPI协议读写寄存器实现复杂的TCP UDP等网络协议。当然带宽会受限于SPI接口有效速率,本文采用芯片为W5500,支持10M/100M自适应,其理论值高达80Mbps,基本达到算法验证的要求。

一、前言