赛灵思 Versal:单芯片内的精准同步

judy 在 周二, 07/27/2021 - 15:43 提交

从金融、电信、工业、消费到航空航天与国防以及汽车,如今,“同步”这个概念,在所有行业无处不在。众多应用完全离不开同步;本文将探讨其中的部分应用并根据这些示例来分享同步这个概念。此外,本文的第二部分将研讨同步的两个关键技术指标:精度与准确性和集成。

从金融、电信、工业、消费到航空航天与国防以及汽车,如今,“同步”这个概念,在所有行业无处不在。众多应用完全离不开同步;本文将探讨其中的部分应用并根据这些示例来分享同步这个概念。此外,本文的第二部分将研讨同步的两个关键技术指标:精度与准确性和集成。

科研仪器成本高昂。研究人员如果想要在实验室里测量 13 种不同参数,就需要 13 种不同的工具。而且随着越来越多的研究人员、工程师和学生需要开展远程协作,为每个人配备必要工具来完成工作的成本也会迅速增加。Liquid Instruments 意识到了这一挑战,并决定开发出一套解决方案,使用由软件定义的硬件将多种工具集成为单个工具,改变测试测量的方式。

Kintex UltraScale+ 拥有的高速 SerDes,大大简化了 PCB 设计、节约了 PCB 面积;其片内集成大量 Block RAM、UltraRAM,替代了传统方案中的多片外挂 QDR SRAM,从而大幅节省 IO 资源和 PCB 面积。Kintex 器件所拥有的高速处理时钟和丰富的 DSP 资源,满足了数字示波器宽带实时数字信号处理,复杂滤波,高速 FFT 需求。

2021 赛灵思技术日是一场以“自适应”技术为平台的线下深度互动会议,是软件/硬件研发人员、算法开发、系统架构师的专属会议。在这里,您可以看到最新的产品工具介绍、方案与 IP 更新、应用实例展示等内容,更可以与专家面对面深入探讨从设计技巧、系统性能到架构优化等话题。

本届 CVPR 上,来自北京的赛灵思 AI 研发团队的论文《RankDetNet:深入研究目标检测中的排序约束》成功入选。同时,在 CVPR 期间的自动驾驶研讨会“ Waymo 开放数据集挑战赛”上,赛灵思北京 AI 研发团队又获得“实时 3D 检测”第三名。

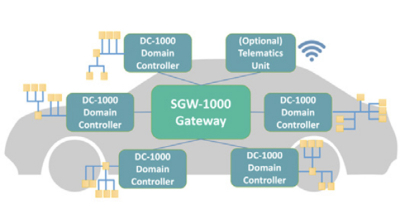

目前,汽车市场对软件定义功能和应用的需求越来越旺盛,行业正迫切需要一种先进的网关,能够提供通用性并为客户提供数据加速和数据分析功能。此外,由于 OEM 车辆和软件定义车辆在需求上存在较大差异,因此需要一种功能更强大且良好平衡的通用型解决方案。

赛灵思近日宣布推出 Vivado® ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

赛灵思公司今日宣布推出 Vivado® ML 版,这是业内首个基于机器学习( ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本。与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

Kria K26 SOM 旨在帮助数百万开发人员在其首选设计环境中使用开箱即用的低成本开发套件更快地部署他们的智能视觉应用程序。

边缘端需要低时延、AI算力、低功耗、安全与保密,将全新Versal平台带到边缘会怎样?