Verilog语法之条件编译指令`ifdef, `ifndef,`else, `elsif, `endif

judy 在 周二, 12/13/2022 - 16:44 提交

Verilog的编译和C语言的编译二者自然不可同日而语,具体到FPGA的开发

Verilog的编译和C语言的编译二者自然不可同日而语,具体到FPGA的开发

本文一起介绍这3个语句的应用场景和应用方法

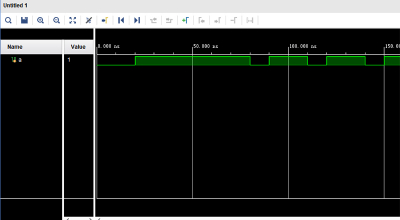

系统任务$finish的作用是退出仿真器,结束仿真过程

与C语言中的函数类似,在Verilog代码中,通过把代码分成小的模块或者使用任务(task)和函数(function)

前面介绍了CityHash32中前3种场景下的算法实现,这里继续介绍最后一种,也是最复杂的一种

Hash是FPGA设计中非常常见的一个功能。它是将一个Mbyte长度的数据通过hash计算变成一个Nbyte长度的数据

无论是FPGA还是ASIC的开发者,都或多或少地做过代码检视(code review)。

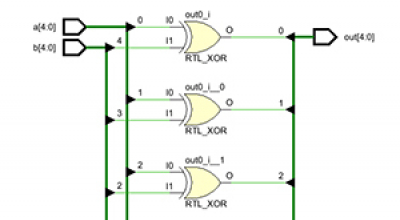

在FPGA编码的时候,如果多使用生成块语句,敲代码的时间大大减少。但是,代码的可读性会更高。

case语句可以说是我们在FPGA开发中使用频率非常高的一条语句。同时,Verilog还提供了语句 casex 和 casez供我们使用。

当我们使用Verilog时,对于信号定义为reg型还是wire型比较混乱,那么今天我们就来讲一讲如何快速的进行信号定义。