ZYNQ HDMI输出实验——FPGA Vitis篇

judy 在 周二, 05/30/2023 - 10:09 提交

本实验使用FPGA通过HDMI接口输出彩条、色带、方块等图像。

本实验使用FPGA通过HDMI接口输出彩条、色带、方块等图像。

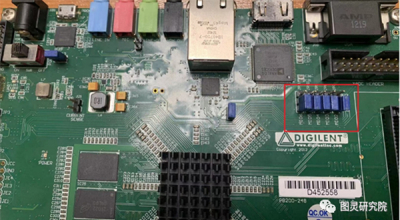

本实验教程主要指导大家如何将程序固化到QSPI FLASH中,并让ZYNQ芯片上电启动自动加载QSPI中的程序

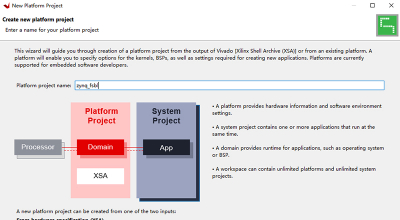

本实验将为大家介绍如何在Vivado中构建 AXI总线类型的IP核

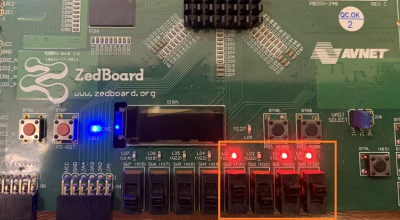

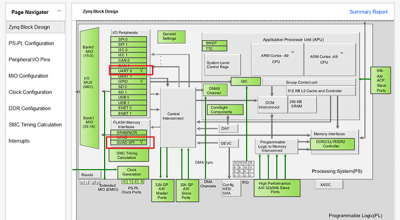

使用ZYNQ最大的疑问就是如何把PS和PL结合起来使用。本实验使用两个AXI GPIO的IP核

本实验介绍如何使用ZYNQ芯片PS端的定时器资源

本实验主要介绍使用PS端来完成ZYNQ串口打印输出的功能

本文主要针对使用GD(兆易创新)系列的FLASH做启动配置片时,遇到的相关问题进行简单整理复盘

从音频输入到输出,现有的实时数字音频系统很难实现低于 1ms 的时延

本文将无DDR固化的情况进一步进行介绍,讲解如何修改FSBL实现ZYNQ的程序固化

本教程提供 VITIS 2021.1 QSPI-FLASH 下载方法如下