Zynq AXI-ACP接口简介

judy 在 周三, 06/09/2021 - 16:53 提交

ZYNQ中的AXI接口包含三个类型,共9个,主要用于PS与PL的互联。今天我们重点来说一下ACP接口。

ZYNQ中的AXI接口包含三个类型,共9个,主要用于PS与PL的互联。今天我们重点来说一下ACP接口。

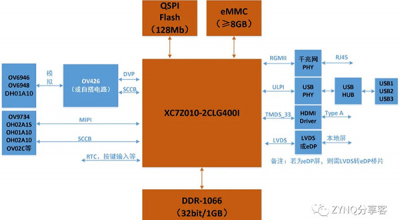

这一次,熊猫君分享一个内窥镜的技术实现方案。内窥镜的方案很多:主处理器有用专用ASIC的,比如日、台、韩的相机ASIC;有用专用CPU的,比如海思、瑞星微和君正等。熊猫君的这个是基于Xilinx ZYNQ的低成本方案。

利用SDR做一个收音机是所有入门SDR都会做的小项目,简单直观易上手的特点和“Hello World”、流水灯一样。本篇文章就带领大家利用AD936X+ZYNQ平台SDR做个SDR。

对于GP接口(general purpose)通用目的接口,有四个接口(两个从端口,两个主端口)。GP接口直接连接到的是中央互联区(central interconnect),然后由中央互联区再连接到OCM interconnect和存储器接口上。对于GP接口,通常使用他进行控制配置。

这次分享一个在Xilinx FPGA实现MIPI DPHY接口的案例(包括CIS协议层)。截止目前为止,Xilinx仅在Ultrascale+及其以上版本的FPGA IO可直接支持MIPI 电平输入,其他的,都需要转换成LVDS来接收。

为满足合成孔径雷达实时成像、数据回放等高速可靠数据传输需求,解决传统数据传输系统由于接口要求高、体积与功耗大以及网络配置不灵活等原因不适合用于外场试验的问题,基于 ZYNQ 芯片设计一种光纤接口到以太网接口的数据传输系统。主要介绍数据传输流程的实现方法,并提出一种三级乒乓和指令并行的优化策略保证数据正确,提高传输速度

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将硬件比特流文件(.bit)和软件的可执行链接文件(.elf)下载到 Zynq 开发板中,这样就可以对自己的软硬件设计进行调试和验证。

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中需要对IIC接口进行初始化在黑金和米联的例程里为了方便用户使用,对IIC和外设设备分别创建了相应的文件方便用户开发。

在ZYNQ的体系结构中定时器太丰富了,而大量的教程中基本就只玩了私有定时器,可以中断就OK了。其实在ZYNQ中定时器资源很丰富,每个CPU有自己的私有定时器和看门狗,有一个所有CPU共享的全局定时器和看门狗,两个三路定时器还有AXI_TIMER的IP可用,不过好像很少有博客把这些测试完。

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口