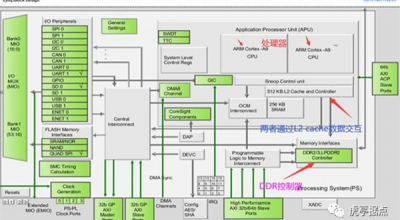

Vivado中ZYNQ详解(主要用于PS和PL之间的工作衔接)

guanxiao_505740 在 周三, 07/29/2020 - 10:38 提交

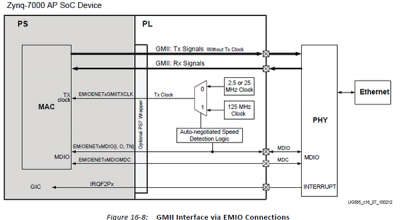

AXI(Advanced extensible Interface)协议主要描述了Master设备和Slave设备之间的数据传输方式,Master设备和Slave设备之间通过握手信号建立连接。当Slave设备的数据准备好时,会发出和维持VALID信号,表示数据有效;当Master设备准备好接收数据时,会发出READY信号。数据只有在这两个信号都有效时才开始传输。