下载全新 AMD Vivado™ Design Suite 2025.1 版

judy 在 周五, 06/13/2025 - 09:42 提交

AMD Vivado™ Design Suite 2025.1 现已推出,支持 AMD Spartan™ UltraScale+™ 和新一代 Versal™ 器件。

AMD Vivado™ Design Suite 2025.1 现已推出,支持 AMD Spartan™ UltraScale+™ 和新一代 Versal™ 器件。

通过全新资源中心,可轻松访问丰富的教程、演示及更多资源。参阅实用指南和真实设计示例,快速调试硬件可编程逻辑设计。

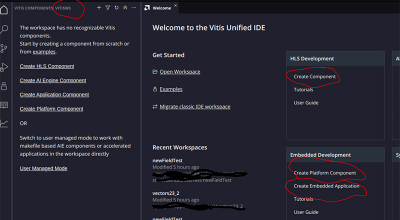

这篇博客是在上一篇博客 Vitis HLS 系列 1 的基础上撰写的,但使用的是 Vitis Unified IDE,而不是之前传统版本的 Vitis HLS。

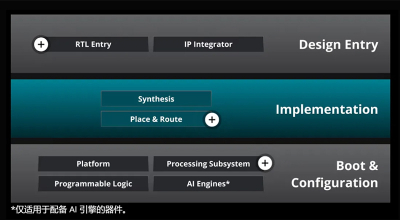

AMD Versal自适应 SoC 架构通过异构加速和硬 IP集成提供卓越的系统性能功耗比。但当开发者想从上一代 FPGA 迁移时如何确保最佳结果呢?

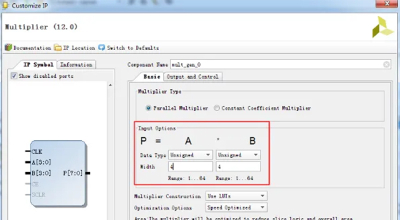

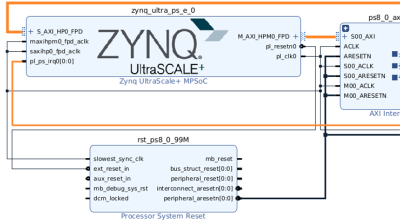

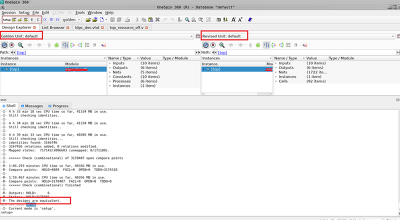

今天给大侠带来Vivado调用IP核详细操作步骤,手把手教学,请往下看。话不多说,上货。

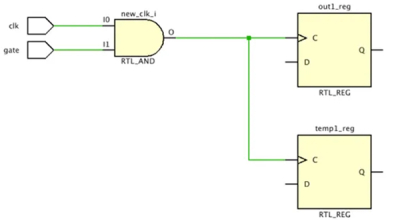

传统上,使用门控时钟是 ASIC 设计中降低系统功耗的常见方法。通过门控时钟,可在非必要时阻止整组寄存器的状态转换。

Vivado 设计套件提供经过优化的设计流程,让传统 FPGA 开发人员能够加快完成 Versal 自适应 SoC 设计。

这篇博客旨在逐步演示如何使用 Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器

本文讲述了如何使用 One Spin 检查 AMD Vivado™ Design Suite Synth 的结果(以 Vivado 2024.2 为例)。

了解 AMD Versal 产品组合与前几代 FPGA 相比在时钟架构功能的增强,并了解如何利用 AMD Vivado™ 工具的先进功能快速完成设计并实现性能目标。